# Engineering a Subnanometer Interface Tailoring Layer for Precise Hydrogen Incorporation and Defect Passivation for High-End Oxide Thin-Film Transistors

Jong Beom Ko, Seong-In Cho, and Sang-Hee Ko Park\*

| Cite This: https://doi.org/10.1021/acsami.3c10185 |                    | 85 | Read Online               |  |                        |  |

|---------------------------------------------------|--------------------|----|---------------------------|--|------------------------|--|

| ACCESS                                            | III Metrics & More |    | E Article Recommendations |  | Supporting Information |  |

**ABSTRACT:** Top-gate self-aligned structured oxide thin-film transistors (TFTs) are suitable for the backplanes of high-end displays because of their low parasitic capacitances. The gate insulator (GI) deposition process should be carefully designed to manufacture a highly stable, high-mobility oxide TFT, particularly for a top-gate structure. In this study, a nanometer-thick  $Al_2O_3$  layer via plasma-enhanced atomic layer deposition (PE-ALD) is deposited on the top-gate bottom-contact structured oxide TFT as the interface tailoring layer, which can also act as the hydrogen barrier to modulate carrier generation from hydrogen incorporation into the active layer of the TFT during the following process such as postannealing. Al-

doped InSnZnO (Al/ITZO) with an Al/In/Sn/Zn atomic ratio composition of 1.7:24.3:40:34 was used for high mobility oxide semiconductors, and an  $Al_2O_3/Si_3N_4$  bilayer was used for the GI. The degradation issue due to the excellent barrier characteristics of  $Al_2O_3$  and  $Si_3N_4$  can be minimized. An oxide TFT fabricated without the interface tailoring layer exhibits conductor-like characteristics owing to the excessive carrier generation by hydrogen incorporation. However, TFTs with additional interface layers exhibit reasonable characteristics and distinct trends in electrical characteristics depending on the thicknesses of the interface layers. The optimized devices exhibit an average turn-on voltage ( $V_{on}$ ) of -0.31 V with 33.63 cm<sup>2</sup>/(V s) of high mobility and 0.09 V/dec of subthreshold swing value. The interfaces between the active layer and hydrogen barriers were investigated using a high-resolution transmission electron microscope, contact angle measurement, and secondary ion mass spectroscopy to reveal the origin of the trends in properties between the devices. The top-gate device with a hydrogen barrier using the four-cycle deposition exhibits optimum electrical characteristics of both high mobility and good stability with only a 0.04 V shift of  $V_{on}$  under positive-bias temperature stress (PBTS). We realize a high-end, self-aligned TFT with high mobility [34.7 cm<sup>2</sup>/(V s)] and negligible  $V_{on}$  shift of -0.06 V under PBTS by applying a subnanometer hydrogen barrier.

KEYWORDS: carrier control, defect passivation, stability, high mobility, oxide thin-film transistor (TFT), atomic layer deposition (ALD)

## 1. INTRODUCTION

Active-matrix organic and microlight-emitting diodes form the leading next-generation display owing to their vivid color, high efficiency, excellent contrast ratio, flexibility, and lightness.<sup>1–3</sup> They can be suitably applied in high-end, large-area, form-valuable displays. Backplane devices have to be uniform over a large area to drive numerous pixels within a short time for high-resolution and large-area displays. Thin-film transistors (TFTs) with oxide semiconductors satisfy these requirements owing to their outstanding electrical characteristics, processability over large areas with good uniformity, and easy fabrication.<sup>4–6</sup>

Several oxide semiconductors, such as indium zinc oxide (IZO),<sup>7</sup> indium oxide (InO),<sup>8</sup> indium tin zinc oxide (ITZO),<sup>9</sup> indium gallium tin oxide (IGTO),<sup>10</sup> and Al-doped ITZO (Al/ITZO),<sup>11</sup> are known to have high mobility. The stoichiometry of oxide semiconductors is crucial in electrical character-ization,<sup>12</sup> and the mobility of oxide semiconductors can be further improved by optimizing the composition.<sup>13</sup> These

oxide semiconductors are easily and uniformly deposited by sputtering for high-end display backplanes. Among various oxide TFT structures, a self-aligned structure offers the advantage of reduced resistance–capacitance delay that is generated by the parasitic capacitance between the gate and source/drain, irrespective of the gate insulator (GI).<sup>14–16</sup> Additionally, a high on-current can be obtained with a selfaligned structure using a GI of high-k materials, such as HfO<sub>2</sub><sup>17</sup> and Y<sub>2</sub>O<sub>3</sub>.<sup>18</sup> Furthermore, to prevent the thermionic emission of electrons and holes from the oxide semiconductor to the insulator owing to the low band offset and Al<sub>2</sub>O<sub>3</sub><sup>19</sup> multilayers,

Received: July 15, 2023 Accepted: September 18, 2023

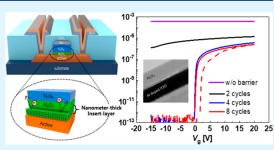

Figure 1. Schematic of a high-mobility TFT with an ultrathin hydrogen barrier layer.

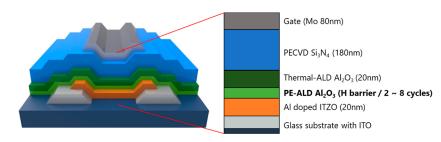

Figure 2. Transfer characteristics of TFTs with different thicknesses of barrier conditions: (a) before annealing, (b) after vacuum annealing at 330 °C, and (c) after vacuum annealing at 350 °C. The trends of (d) field-effect mobility and (e) hysteresis are based on the thermal annealing temperature.

such as  $Al_2O_3/Si_3N_4^{3,20}$  bilayers, or multicomponent doping have been investigated.<sup>21</sup> However, realizing reasonable electrical characteristics of high-mobility oxide TFTs with a top-gate structure is challenging. Because a GI is deposited on an oxide semiconductor in the top-gate structure, the doping effect of hydrogen during GI deposition and subsequent processes, including postannealing, cannot be avoided. In particular, the GI deposition process must be carefully designed in terms of hydrogen incorporation, while fabricating oxide TFTs with high mobility and stability. Although this phenomenon renders the yield of normal transfer characteristics in high-mobility oxide TFT complex owing to the creation of excessive carriers, 22-24 it passivates traps to improve the electrical reliability of the TFTs.<sup>25,26</sup> Therefore, hydrogen incorporation must be appropriately controlled. Studies to improve the electrical characteristics of oxide TFTs by incorporating hydrogen through gas annealing<sup>27</sup> or plasma treatment are underway.<sup>26,28</sup> However, novel methodologies to precisely control the incorporation of hydrogen are required because the  $V_{\rm on}$  characteristic is very sensitive to the amounts of hydrogen in high-mobility oxide TFTs. In this study, ultrathin additional layers were applied between the active

layer and GI as the novel methodology for the precise control of hydrogen incorporation.

We fabricate high-end, top-gate-structured oxide TFTs with an  $Al_2O_3/Si_3N_4$  bilayered GI.<sup>3,20</sup> We modulate the amount of hydrogen diffused from the  $SiN_x$  into the active layer by utilizing Al<sub>2</sub>O<sub>3</sub>, which is deposited using a combination of plasma-enhanced atomic layer deposition (PE-ALD) and thermal ALD. An ALD process can be classified into thermal and PE-ALD, which use  $H_2O$  as the oxidant and  $O_2$  plasma, respectively. Thermal ALD causes a large amount of hydrogen incorporation owing to the H2O oxidant. Based on a preliminary study, the use of thermal-ALD-processed Al<sub>2</sub>O<sub>3</sub> film as the GI of oxide TFT degraded the transfer characteristics of oxide TFTs because of hydrogen incorporation.<sup>3</sup> In this study, an ultrathin layer of  $Al_2O_3$  is deposited by PE-ALD as a hydrogen barrier before further deposition by thermal-ALD resulting in hydrogen incorporation. The electrical characteristics of the fabricated TFTs are investigated relative to the interface layer deposited by PE-ALD. We performed high-resolution transmission electron microscopy (HRTEM), contact angle measurements, and secondary ion mass spectroscopy (SIMS) to validate the differences in the

electrical characteristics of the TFTs and the effects of the hydrogen barrier. We achieve high-mobility oxide TFTs with stable characteristics by controlling hydrogen incorporation through the deposition of a nanometer-thick barrier layer by PE-ALD.

#### 2. EXPERIMENTAL SECTION

Top-gate bottom-contact TFTs were fabricated under different GI deposition conditions. Because top-gate bottom-contact TFTs have the same stacking sequence of active layers and GIs as those of self-aligned TFTs, they are suitable for investigating the effects of GIs and their deposition processes on the electrical characteristics of oxide TFTs. Each layer was aligned using photolithography with a photo mask for the fabrication of the devices.

Indium tin oxide was patterned as the source and drain, and 20 nm of Al/ITZO, which is an actively researched high-mobility oxide semiconductor,<sup>11</sup> was deposited via sputtering. The comparison of the electrical characteristics of the Al/ITZO and other researched oxide semiconductors is listed in Table S1.<sup>3,8,11,13,29–31</sup> While Al/ITZO did not reach the high-mobility characteristics of ALD-processed a-IGZO with optimized composition,<sup>13</sup> it exhibited mobility of approximately 30  $\text{cm}^2/(\text{V s})$ , similar to well-known high-mobility oxide semiconductors, such as IZO, InOx, and ITZO. Furthermore, Al/ITZO demonstrates good endurance against chemicals, such as photoresist (PR) and PR stripper.<sup>11</sup> Therefore, the effects of the GI process should be investigated preferably by excluding the side effects of chemical damage. A stack of 20 and 180 nm Al<sub>2</sub>O<sub>3</sub> and Si<sub>3</sub>N<sub>4</sub>, respectively, was adopted as the GI because these structures have been reported as attractive GIs for high-end devices.<sup>3,20</sup> At 200 °C, the Al<sub>2</sub>O<sub>2</sub> layer was deposited via thermal-ALD with a trimethylaluminum precursor as the Al source, whereas the Si<sub>3</sub>N<sub>4</sub> layer was deposited by plasma-enhanced chemical vapor deposition (PE-CVD). To mitigate the incorporation of hydrogen, an ultrathin Al<sub>2</sub>O<sub>3</sub> layer was deposited via PE-ALD as a hydrogen barrier prior to GI deposition. The electrical characteristics of the devices were investigated based on the number of deposition cycles of the hydrogen barrier, with two, four, and eight cycles of PE-ALD. Growth per cycle (GPC) was used to calculate the hydrogen barrier thicknesses as 0.25, 0.5, and 1.0 nm, respectively. Finally, Mo, a widely used electrode material, was deposited and patterned as the gate electrode.<sup>32</sup> A schematic of the fabricated oxide TFT is shown in Figure 1. The fabricated TFTs were annealed at 330 and 350 °C under vacuum conditions. The electrical and stability characteristics of the devices were investigated in dark conditions to exclude the light radiation effect using the Agilent 4284A precision LCR meter and B4156A semiconductor parameter analyzer with a probe station.<sup>33,34</sup> The interfaces between the active layer and GIs were scrutinized with HRTEM, contact angle measurements, and SIMS to investigate the origin of the differences in the electrical characteristics of the TFTs.

#### 3. RESULTS AND DISCUSSION

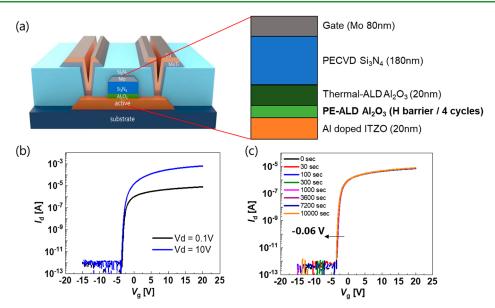

The fabricated devices showed distinct trends in electrical characteristics depending on the thickness of the hydrogen barrier. The transfer characteristics and electrical parameters of each TFT based on the thermal annealing conditions are shown in Figure 2. (12 overlapped transfer characteristics in the linear and saturation regions for each sample after thermal annealing at 350 °C are shown in Figure S1 in the Supporting Information). A drain voltage  $(V_d)$  of 0.1 V was applied to the TFT with a length and width of 40 and 20  $\mu$ m, respectively. The solid and dashed lines on the graph represent the forward and reverse sweeps, respectively. The oxide TFT without the hydrogen barrier struggled to exhibit normal ON/OFF characteristics owing to excessive hydrogen incorporation from the following processes, as shown in Figure 2. Additionally, the oxide TFT with two cycles of hydrogen barrier showed conductive or negatively shifted characteristics,

indicating the insufficiency of the two cycles of PE-ALDdeposited Al<sub>2</sub>O<sub>3</sub> to prevent hydrogen incorporation from processes, such as GI deposition and postannealing. In addition, the device with two cycles of barrier exhibited conductor-like behavior in as state. Sputtered oxide semiconductors require a further activation process through thermal annealing to stabilize the channel against the generated scattering center, ionized oxygen vacancies  $(V_0^+)$ , and weak oxygen bonding.<sup>35</sup> Furthermore, in the top-gate structure, the GI and gate metal deposited on top of the active layer expose the oxide semiconductor to UV irradiation during plasma of the CVD process and sputtering for the GI and gate metal deposition, respectively. This UV exposure results in carrier generation and facilitates the formation of the conductive channel.<sup>30,33</sup> After thermal annealing at 330 °C, the devices exhibited ON/OFF characteristics owing to the activation of the oxide semiconductor by thermal energy, restoration of generated free carriers by UV, and curing of donor-like defects, such as  $V_o$  and weakly bonded O–H.<sup>36,37</sup> Further annealing at a higher temperature of 350 °C resulted in more hydrogen diffusion into the oxide semiconductor and generated free carriers, resulting in conductive behavior. The devices with four and eight cycles of the hydrogen barrier process exhibited ON/OFF characteristics prior to thermal annealing owing to the thicker barrier compared to those of two cycles. This resulted in a reduced hydrogen incorporation. In addition, the high OFF current indicates that sputtered oxide semiconductors required an additional activation process with thermal energy, as earlier mentioned. After thermal annealing, the devices showed reasonable transfer characteristics. Particularly, the oxide TFT with four hydrogen barrier cycles exhibited exceptional transfer characteristics, whereas that with eight hydrogen barrier cycles exhibited hysteresis-like characteristics. The devices exhibit increased conductivity as the annealing temperature increased from 330 to 350 °C. Thermal annealing induces hydrogen diffusion from the GI to the active layer, which can be enhanced at a higher temperature because hydrogen diffusivity generally increases with temperature.<sup>38</sup> In general, hydrogen increases carrier density in oxide semiconductors by acting as a shallow donor.<sup>22-24</sup> Consequently, the conductivity of the devices is increased, owing to the increase in free carriers.

The results of the extracted electrical parameters obtained based on thermal annealing are shown in Figure 2d,e. The value of  $\mu_{\rm FE}$  was calculated as follows

$$\mu_{\rm FE} = \frac{g_{\rm m}}{\frac{W}{L} \times C_{\rm i} \times V_{\rm d}} \quad \left( \text{where } g_{\rm m} \equiv \frac{\partial I_{\rm d}}{\partial V_{\rm g}} \right) \tag{1}$$

where W and L denote the channel width and length, respectively, and  $C_i$  is the capacitance of the GI; the measured value of the double-layered GI was approximately 3.1 pF/m<sup>2</sup>. The electrical properties of the devices improved with an increase in the thermal annealing temperature because hydrogen diffusion increased from the thermal-ALD Al<sub>2</sub>O<sub>3</sub> layer, through the hydrogen barrier (deposited by PE-ALD), into the oxide semiconductor, resulting in the passivation of more defects. The PE-ALD process utilized for the hydrogen barrier can induce plasma damage and generate shallow defects, resulting in clockwise hysteresis. However, these defects can be effectively passivated by hydrogen incorporation.<sup>39</sup> A thicker hydrogen barrier could result in a larger number of defects remaining unpassivated by inhibiting hydrogen diffusion into the oxide semiconductor. In addition, more shallow defects are generated owing to the employment of more hydrogen barrier cycles. Consequently, the device with eight hydrogen barrier cycles exhibits a relatively large hysteresis with a value of 0.49 V. The extracted average values of electrical parameters for 12 devices are listed in Table 1. The devices with four hydrogen barrier cycles exhibit optimized electrical characteristics with a high mobility of 33.63 cm<sup>2</sup>/(V s) and negligible hysteresis.

Table 1. Extracted Electrical Parameters with Average and Standard Deviation for 12 Devices with Different Barrier Thicknesses after Vacuum Annealing at 350 °C

| cycles of<br>barriers<br>[cy] | $V_{\rm on}$ [V] | $[\mathrm{cm}^2/(\mathrm{V~s})]$ | SS [V/dec]      | hysteresis [V]   |

|-------------------------------|------------------|----------------------------------|-----------------|------------------|

| 2                             | NA               | NA                               | NA              | NA               |

| 4                             | $-0.31 \pm 0.16$ | $33.63 \pm 0.82$                 | $0.09 \pm 0.01$ | $0.035 \pm 0.03$ |

| 8                             | $-0.08 \pm 0.30$ | $22.61 \pm 1.09$                 | $0.12 \pm 0.01$ | $1.579 \pm 0.55$ |

The hydrogen barriers deposited for this study were thin with thicknesses of less than 1.0 nm. The thin hydrogen barriers were expected to physically block hydrogen and hinder carrier generation through other factors. HRTEM images of cross-sectional oxide semiconductor/ $Al_2O_3$  stacks were analyzed to investigate the interfaces between the oxide semiconductor and  $Al_2O_3$  layer, as shown in Figure 3. While the

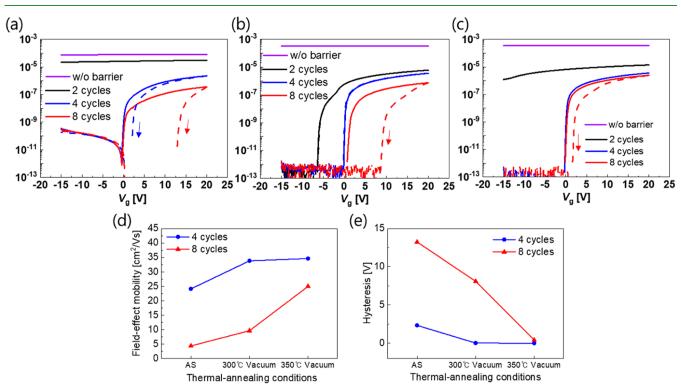

Figure 3. HRTEM images of cross-sectional film stacks with  $Al_2O_3$  deposited by (a) thermal-ALD and (b) PE-ALD.

TEM image showed a clear interface between the thermal-ALD  $Al_2O_3$  layer and oxide semiconductor, an interlayer was observed in the film deposited using PE-ALD. The interlayer reportedly contained defects, including dangling bonds, which resulted in the utilization of incorporated hydrogen to passivate these defects.<sup>40,41</sup> Furthermore, cross-sectional

images were acquired based on the number of cycles of the hydrogen barrier, and the interlayer structure was clearly observed after a few cycles of hydrogen barrier deposition, as shown in Figure S2.

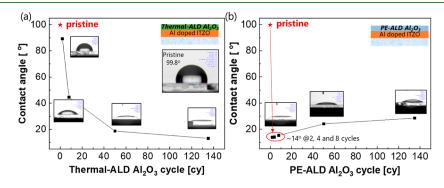

The defective interlayer formation was confirmed by the decrease in the contact angle measured after a few cycles of the  $Al_2O_3$  layer via PE-ALD, as shown in Figure 4. The pristine oxide semiconductor had a contact angle of 99.8°, as shown in the inset of Figure 4a. However, after PE-ALD for  $Al_2O_3$ , the contact angle decreased considerably to less than 15°, whereas a large contact angle was maintained when  $Al_2O_3$  was deposited via thermal ALD. This defect-induced hydrophilic behavior owing to dangling bonds resulted in a small contact angle,<sup>42</sup> thus reducing hydrogen diffusion through the very thin  $Al_2O_3$  layer deposited via PE-ALD and the defective interlayer.

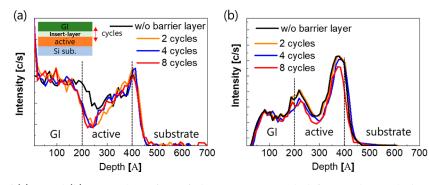

The depth profiles of hydrogen and OH in film samples with the same stack sequence as the fabricated top-gate structured device were investigated by using SIMS, as shown in Figure 5a,b, respectively. The incorporation of hydrogen and OH in the oxide semiconductor decreased with the application of additional hydrogen barriers, meaning the use of a subnanometer thick hydrogen barrier effectively reduced the diffusion of hydrogen into the oxide semiconductor, leading to devices with reasonable transfer characteristics and moderate carrier concentrations. Although only a minor difference in the OH concentration between the samples was observed, the device with two cycles of the hydrogen barrier process showed conductor-like characteristics, whereas those with four and eight hydrogen-barrier cycles exhibited transfer characteristics. The significant difference in electrical characteristics was attributed to the large number of intrinsic carriers in highmobility oxide semiconductors. The degradation of the ON/ OFF characteristics owing to extra carrier generation was more sensitive in high-mobility cases.43 Hence, even in small amounts, hydrogen diffusion must be finely controlled, particularly in high-mobility oxide TFTs. Thus, the adoption of a hydrogen barrier produced by ALD is an appropriate process, owing to its controllable atomic thickness. In fact, no significant difference was observed in the composition of hydrogen based on the cycles of barriers. However, smaller amounts of OH were detected in the oxide semiconductor when thicker barriers were applied. Based on previous studies, hydrogen can exist in various forms within oxide semiconductors, including hydrogen interstitial bonding with oxygen (H<sub>i</sub><sup>+</sup>), bonding with metal (H<sub>i</sub><sup>-</sup>), combined with  $V_o$  $(H_o^+)$ , and complex of  $V_o^0 + H_i^- (H-DX^-)$ .<sup>44,45</sup> Therefore, the hydrogen in oxide semiconductors can exist in various forms,

**Figure 4.** Contact angle variation on the oxide semiconductor surface with cycles of (a) thermal-ALD and (b) PE-ALD for  $Al_2O_3$  layer deposition. The inset indicates the contact angle of the pristine oxide semiconductor.

www.acsami.org

Figure 5. Depth profiles of (a) H and (b) OH in the GI/active/substrate structure with different H barrier thicknesses.

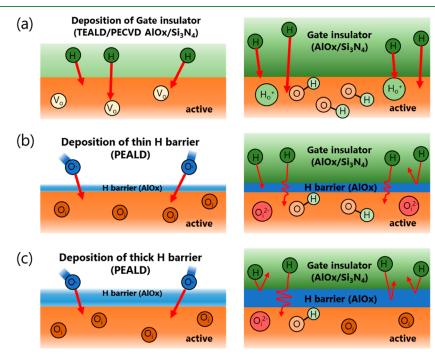

Figure 6. Illustration of a possible hydrogen incorporation mechanism in the case of (a) without an additional barrier and (b) with thin and (c) thick hydrogen barrier deposition processes.

Figure 7. Spectra of XPS O 1s for the active layer surface (a) without additional barrier, (b) with two cycles, (c) four cycles, and (d) eight cycles of the barrier.

including both hydrogen and OH. However, distinguishing the different bonding forms of the hydrogen analyzed by SIMS is challenging because the high-energy secondary ions used in the measurement can break the bonding of the elements. However, the bonding between O–H is quite strong compared with the hydrogen in  $V_o$  sites, indicating that much of the hydrogen detected by SIMS is likely combined with  $V_o$  and the hydrogen bonding with oxygen is detected in the form of OH.<sup>44</sup> As

shown in Figure 6a, without additional barriers, hydrogens can be easily introduced into the oxide semiconductor and placed in  $V_o$  sites or bonded with oxygen. Therefore, a relatively large amount of both hydrogen and OH was detected in the SIMS depth profile. In contrast, when additional barriers were applied, the negligible difference in the hydrogen depth profile suggested that the  $V_o$  state on the active surface remained the same regardless of the cycles of the hydrogen barrier. This is

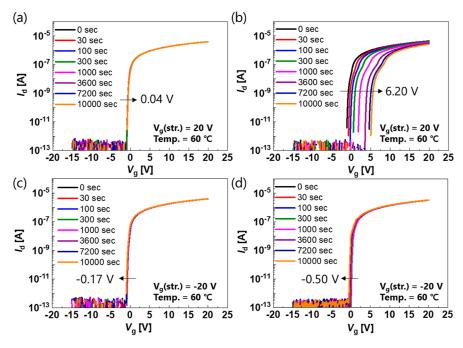

Figure 8. Evaluation of device transfer curves with (a,c) four and (b,d) eight hydrogen barrier cycles under PBTS ( $V_{gstr} = 20$  V, Temp. = 60 °C) and NBTS ( $V_{gstr} = -20$  V, Temp. = 60 °C).

because even a few cycles of the PE-ALD process could inject sufficient oxygen into the underlying oxide semiconductors during oxygen plasma, reducing the  $V_o$  states as shown in Figure 6b,c. Consequently, the differences in the degree of hydrogen incorporation were primarily observed in the OH depth profile rather than in the hydrogen depth profile. Although hydrogen and OH rapidly increased at the substrate interface owing to the interface effect in SIMS, it is clearly observed that the hydrogen incorporation tends to decrease as the thickness of the barrier increases.<sup>46</sup>

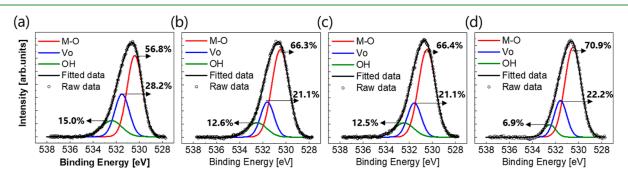

X-ray photoelectron spectroscopy (XPS) analysis was conducted to validate the effect of hydrogen barrier deposition on the oxygen bonding state in the oxide semiconductors. We scrutinize the O 1s peaks of the film samples with the same stack sequence as the fabricated top-gate structured device, according to the hydrogen barrier cycles at the surface region of oxide semiconductors. The O 1s peaks were deconvoluted into the metal-oxygen bonding (M-O),  $V_0$ , and OH centered at 530.4  $\pm$  0.1, 531.5  $\pm$  0.1, and 532.5  $\pm$  0.1 eV, respectively, as shown in Figure 7. $^{35,47}$  The portion of V<sub>o</sub> decreased from 28.2% to approximately 21% when hydrogen barriers applied. Notably, the deposition process of two cycles of hydrogen barrier effectively reduced Vo, and it barely changed with increasing cycles of hydrogen barriers. Therefore, a similar hydrogen depth profile was observed in the SIMS results, owing to the negligible difference in V<sub>o</sub> sites within the oxide semiconductor according to the thickness of the hydrogen barrier. The difference in the degree of incorporated hydrogens according to the thickness of the hydrogen barrier was observed in OH depth profiles, which was also validated in the XPS results. The portion of OH in the O 1s peaks decreased from 12.5 to 6.9% as the cycles of hydrogen barriers increased from two to eight cycles. In summary, an increase in the cycle of the hydrogen barrier decreased the total amount of hydrogen introduced to oxide semiconductors.

The transfer characteristics and stability of high-mobility oxide TFTs were significantly influenced by the thickness of the hydrogen barrier. The overlapped transfer curves obtained under positive-bias temperature stress (PBTS) and negativebias temperature stress (NBTS) conditions are shown in Figure 8. The transfer characteristics of the oxide TFTs with four hydrogen barrier cycles barely changed under PBTS, whereas the transfer curve shifted significantly in the positive direction when a thicker hydrogen barrier of eight cycles was used, as shown in Figure 8a,b. The time dependence of  $V_{on}$ under PBTS and stretched exponential fitting is shown in Figure S3. The device with four hydrogen barrier cycles exhibited a 0.05 V shift in  $V_{\rm on}$  after 10 000 s under PBTS, whereas after days, a shift of 0.18 V was expected under PBTS, extracted by the stretched exponential fitting. The difference in the electrical reliability of the devices resulted from variations in hydrogen and the excess oxygen incorporation into the active layer. Numerous studies explored the role of hydrogen as a defect passivator and improvements in electrical stability.<sup>25,26</sup> According to the studies, hydrogen passivates electron-trap sites by bonding with structural defects, such as dangling bonds, or acceptor-like traps, such as oxygen interstitials (O<sub>i</sub>). From the possible mechanism in Figure 6b,c, during the deposition of hydrogen barriers, excess oxygen can be introduced to oxide semiconductors owing to oxygen plasma, as validated by results of the comparison in the XPS O 1s peaks. When an optimized thickness of the hydrogen barrier was adopted (four cycles), a moderate amount of hydrogen was incorporated, which passivated the defect states by ionizing the O<sub>i</sub> or bonding with dangling bonds.<sup>45,48</sup> The ionized O<sub>i</sub> could not trap further free electrons, resulting in the TFT with four cycles of the barrier exhibiting good PBTS stability. In contrast, when a thicker hydrogen barrier was applied, fewer hydrogens were introduced, and more structural or acceptor-like defects remained unpassivated, as shown in Figure 6c. Therefore, the device with eight cycles of barrier exhibited degraded stability under PBTS. In addition, the device with eight hydrogen barrier cycles exhibited hump generation during the PBTS, indicating that the additional creation of new acceptor-like states and induced oxygen was crucial in V<sub>th</sub> instability and the hump characteristics.<sup>49</sup> The varying stability results were attributable to the modulation of hydrogen, achieved through the use of an atomically thick hydrogen barrier, which effectively passivated trap sites while maintaining the ON/OFF characteristics of the TFT. In the case of NBTS stability, both devices with four and eight hydrogen barrier cycles exhibited a small change in  $V_{on}$ , as shown in Figure 8c,d, attributed to fewer holes compared with electrons in n-type oxide semiconductors.<sup>50</sup> However, V<sub>o</sub> acted as a hole trap center and induced a negative shift during NBTS.<sup>51</sup> From the previous XPS results, the V<sub>o</sub> sites were effectively reduced during hydrogen barrier deposition through the oxygen plasma. Consequently, both devices with four and eight hydrogen barrier cycles barely showed changes in  $V_{on}$ under NBTS.

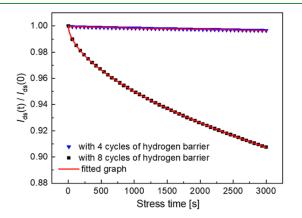

Furthermore, we investigated the decrease in drain current during on-state bias, which resulted in variations in the brightness of the current-driven displays. To measure the normalized change in drain current, we applied biases of  $V_d = 5.5$  V and  $V_g = 5$  V, which corresponded to the saturation region (the output characteristics of the measured devices are shown in Figure S5). The results in Figure 9 showed a decrease

**Figure 9.** Decay of the normalized drain current during bias stress and fitted curves with stretched exponential formulas.

in drain current under an on-bias condition owing to the screening of the gate bias by the trapped charges. The oncurrent decay was modeled using a stretched exponential equation, as follows

$$\frac{I_{\rm D}(t)}{I_{\rm D}(0)} = \exp\left[-\left(\frac{t}{\tau}\right)^{\beta}\right]$$

(2)

where  $I_{\rm D}(0)$  denotes the initial state of the drain current (t = 0),  $\beta$  is the dispersion parameter related to the trap distribution, and  $\tau$  is the characteristic time for carrier trapping. The red lines in Figure 9 represent the fitting results obtained from eq 2. The results were in good agreement with our experimental results. Thus, current decay measurements supported the stretched exponential model, indicating the dominant cause of these instabilities as charge trapping at the defect sites.<sup>52–54</sup> The values of  $\tau$  and  $\beta$  were extracted from the fitted curve and are listed in Table 2. The TFT with eight cycles of the thick hydrogen barrier had a considerably higher value of  $\tau$  compared to that of the TFT with four hydrogen barrier cycles. Therefore, TFT with four hydrogen barrier cycles had significantly fewer trap sites.

www.acsami.org

Research Article

Table 2. Extracted Characteristic Time for Trapping  $(\tau)$  and Dispersion Parameters from the Current Decay Results

| cycles of barriers [cy] | τ [s]               | β    |

|-------------------------|---------------------|------|

| 4                       | $2.2 \times 10^{8}$ | 0.64 |

| 8                       | $1.5 \times 10^{5}$ | 0.57 |

| 4<br>8                  |                     |      |

Intrinsic subgap states near the conduction band of each device were investigated using the differential ideality factor technique (DIFT),<sup>55</sup> as shown in Figure 10. The subgap states were extracted and decomposed into relatively deep and tail states as follows

$$g_{\rm A}(E) = N_{\rm TA} \, \exp\left(\frac{E - E_{\rm C}}{kT_{\rm TA}}\right) + N_{\rm DA} \, \exp\left(\frac{E - E_{\rm C}}{kT_{\rm DA}}\right) \tag{3}$$

Figure 10. Subgap states of the devices derived using the DIFT based on the hydrogen barrier conditions.

The fitted results are indicated by red lines in Figure 10, whereas the parameters extracted according to the hydrogen barrier conditions are listed in Table 3. Based on the graph and

Table 3. Comparison of Extracted Sub-Gap StatesParameters According to the Hydrogen Barrier Conditions

| cycles of barriers<br>[cy] | $[{ m cm}^{N_{ m TA}}{ m eV}^{-1}]$ | $kT_{\mathrm{TA}}$ [eV] | $[{ m cm}^{N_{ m DA}}_{ m eV^{-1}}]$ | $kT_{ m DA}$ [eV] |

|----------------------------|-------------------------------------|-------------------------|--------------------------------------|-------------------|

| 4                          | $2.10 \times 10^{18}$               | 0.02                    | $1.71 \times 10^{18}$                | 0.18              |

| 8                          | $2.09 \times 10^{18}$               | 0.02                    | $1.94 \times 10^{18}$                | 0.41              |

extracted parameters, the device with a hydrogen barrier formed by four-cycles PE-ALD had a lower subgap state, particularly in the deep state, which was passivated with hydrogen.<sup>56</sup> Therefore, a relatively higher amount of hydrogen was incorporated into the oxide semiconductor when four hydrogen barrier cycles were applied compared with eight cycles, resulting in a more effective defect passivation. Consequently, the device exhibited highly stable electrical characteristics.

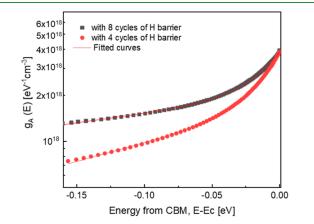

Finally, we fabricated a self-aligned oxide TFT, as shown in Figure 11a. To achieve highly stable high-mobility performance, the hydrogen barrier formed by four cycles of the  $Al_2O_3$ layer via PE-ALD was adopted as the optimal condition and validated in top-gate bottom-contact structured devices. The transfer characteristics for the self-aligned oxide TFT with an optimized hydrogen barrier are shown in Figure 11b, and its electrical parameters are listed in Table 4. The results of the

Figure 11. (a) Schematic of the self-aligned TFT with a hydrogen barrier. (b) Transfer curve of the self-aligned TFT with four hydrogen barrier cycles. (c) Overlapped transfer curve under PBTS of over 10 000 s.

| Table 4. Electrical Parameters of the Self-Aligned TFT with |  |

|-------------------------------------------------------------|--|

| Four Hydrogen Barrier Cycles                                |  |

| SS (V/dec)       | $V_{\rm on}$ [V] | hysteresis [V]   | $\mu_{\rm lin}  [{\rm cm}^2/({\rm V}~{\rm s})]$ |

|------------------|------------------|------------------|-------------------------------------------------|

| $0.13 \pm 0.003$ | $-3.5 \pm 0.29$  | $0.014 \pm 0.04$ | $34.7 \pm 1.25$                                 |

transfer curves of 10 devices overlapped for validation of the reproducibility, as shown in Figure S5. The device exhibited high mobility characteristics of 34.7  $\text{cm}^2/(\text{V s})$ ; however, the I-V curve was slightly shifted in the negative direction. This negative shift was caused by a decrease in the effective channel length owing to the incorporation of hydrogen during the deposition of the interdielectric layer of SiN<sub>1</sub>.<sup>57</sup> The selfaligned oxide TFT demonstrated outstanding stability under PBTS, as shown in Figure 11c, which could be compared with that of a previously evaluated top-gate bottom-contactstructured device. The device also exhibited negligible changes under NBTS owing to fewer defects and holes, as shown in Figure S6. While the top-gate bottom-contact device exhibited normal behavior, the self-aligned oxide TFT showed abnormalities with a slight negative-direction shift in  $V_{\rm on}$ during PBTS. This phenomenon could not be explained by electron trapping during PBTS and was believed to have resulted from other factors. The occurrence of abnormal negative shifts under PBTS owing to the H<sup>+</sup> incorporation into the active layer under PBTS has been investigated. 58,59 In selfaligned structures, more hydrogen was incorporated by lateral diffusion from the interlayer dielectric than that in top-gate bottom-contact structures. This was validated by the  $V_{on}$ characteristics of the initial transfer curve. The top-gate structured device with two hydrogen barrier cycles, with significant hydrogen incorporation, showed results similar to those of the self-aligned structured device. It exhibited a negative shift in V<sub>on</sub> under PBTS, indicating significant hydrogen incorporation. The device with two cycles of the barrier exhibited a negative shift in  $V_{\rm on}$  under PBTS conditions, similar to the self-aligned structure with comparable initial  $V_{on}$ characteristics, as shown in Figure S7. Therefore, the abnormal shift observed under PBTS in the self-aligned device can be

attributed to  $H^+$  incorporation, and it can be improved by optimizing metallization or metal contact.<sup>60,61</sup>

## 4. CONCLUSIONS

We developed highly stable, high-mobility oxide TFTs by adopting subnanometer PEALD-deposited Al<sub>2</sub>O<sub>3</sub> as an interface-tailoring layer to modulate hydrogen incorporation into the channel and defect passivation. A nanometer-thick Al<sub>2</sub>O<sub>3</sub> layer was deposited by a few cycles of PE-ALD and applied as a hydrogen barrier prior to thermal ALD. Oxide TFT without hydrogen barriers struggled to exhibit normal transfer characteristics because of the large amount of incorporated hydrogen. However, devices with additional interface layers exhibited reasonable transfer characteristics. Structural and interface investigations through TEM and contact angle measurements revealed that the formation of defective regions during PE-ALD effectively prevented carrier generation caused by hydrogen incorporation. The electrical characteristics of the devices varied significantly depending on the thickness of the hydrogen barrier. Based on SIMS depth profiles, hydrogen diffusion into the active layer differed depending on the barrier thickness, and O 1s peaks in XPS results indicated that barrier deposition modified the bonding state of oxide semiconductors. When the hydrogen barrier layer deposited by four cycles of the PE-ALD process was adopted, high mobility and high stability characteristics were obtained. Finally, the high-end self-aligned oxide TFT, fabricated with four hydrogen barrier cycles, exhibited a high mobility of 34.7  $\text{cm}^2/(\text{V s})$ , whereas  $V_{on}$  barely shifted under PBTS over 10 000 s at 60 °C.

#### ASSOCIATED CONTENT

### **3** Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsami.3c10185.

Overlapped transfer curves of 12 samples after thermal annealing at 350 °C; HRTEM images of cross-sectional film stacks of the oxide semiconductor and  $Al_2O_3$  layer according to the hydrogen barrier condition; time dependence of  $V_{on}$  under the PBTS condition for

devices with four and eight cycles of hydrogen barriers with stretched exponential fitting; output characteristics of TFTs with four cycles of hydrogen barrier; overlapped transfer curves of 10 self-aligned structured devices with four hydrogen barrier cycles; NBTS stability characteristics of self-aligned oxide TFT; and PBTS stability characteristics of the devices with two cycles of hydrogen barriers, which have similar initial  $V_{\rm on}$  with the self-aligned structured device (PDF)

## AUTHOR INFORMATION

#### **Corresponding Author**

Sang-Hee Ko Park – Department of Materials Science and Engineering, Korea Advanced Institute of Science and Technology (KAIST), Daejeon 305-701, Republic of Korea; orcid.org/0000-0001-7165-8211; Email: shkp@ kaist.ac.kr

#### Authors

Jong Beom Ko – Department of Materials Science and Engineering, Korea Advanced Institute of Science and Technology (KAIST), Daejeon 305-701, Republic of Korea; orcid.org/0000-0002-0073-5918

Seong-In Cho – Department of Materials Science and Engineering, Korea Advanced Institute of Science and Technology (KAIST), Daejeon 305-701, Republic of Korea; orcid.org/0000-0001-6863-6425

Complete contact information is available at: https://pubs.acs.org/10.1021/acsami.3c10185

#### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This study was supported by Samsung Display Co., Ltd.

#### REFERENCES

(1) Hsieh, H.-H.; Lu, H.-H.; Ting, H. C.; Chuang, C.-S.; Chen, C.-Y.; Lin, Y. Development of IGZO TFTs and Their Applications to Next-Generation Flat-Panel Displays. *J. Inf. Display* **2010**, *11*, 160–164.

(2) Wu, T. Z.; Sher, C. W.; Lin, Y.; Lee, C. F.; Liang, S. J.; Lu, Y. J.; Huang Chen, S. W.; Guo, W. J.; Kuo, H. C.; Chen, Z. Mini-LED and Micro-LED: Promising Candidates for the Next Generation Display Technology. *Appl. Sci.* **2018**, *8*, 1557–1617.

(3) Ko, J. B.; Lee, S. H.; Park, K. W.; Park, S. H. K. Interface Tailoring Through the Supply of Optimized Oxygen and Hydrogen to Semiconductors for Highly Stable Top-Gate-Structured High-Mobility Oxide Thin-Film Transistors. *RSC Adv.* **2019**, *9*, 36293–36300.

(4) Kwon, J. Y.; Son, K. S.; Jung, J. S.; Kim, T. S.; Ryu, M. K.; Park, K. B.; Yoo, B. W.; Kim, J. W.; Lee, Y. G.; Park, K. C.; et al. Bottom-Gate Gallium Indium Zinc Oxide Thin-Film Transistor Array for High-Resolution AMOLED Display. *IEEE Electron Device Lett.* **2008**, 29, 1309–1311.

(5) Park, J. S.; Maeng, W. J.; Kim, H. S.; Park, J. S. Review of Recent Developments in Amorphous Oxide Semiconductor Thin-Film Transistor Devices. *Thin Solid Films* **2012**, *520*, 1679–1693.

(6) Kamiya, T.; Nomura, K.; Hosono, H. Present Status of Amorphous In-Ga-Zn-O Thin-film Transistors. *Sci. Technol. Adv. Mater.* 2010, 11 (4), 044305–044323.

(7) Ao, Z. T.; Shan, F.; Guo, H. B.; Kim, H. S.; Lee, J. Y.; Kim, S. J. Indium Zinc Oxide Thin-Film Transistors with Ultraviolet Post-Annealing Treatment. J. Nanosci. Nanotechnol. 2019, 19, 6170-6173. (8) Yeom, H. I.; Ko, J. B.; Mun, G.; Park, S. H. K. High Mobility Polycrystalline Indium Oxide Thin-Film Transistors by Means of Plasma-Enhanced Atomic Layer Deposition. *J. Mater. Chem. C* 2016, 4, 6873–6880.

www.acsami.org

(9) Upadhyay, R.; Steudel, S.; Hung, M.-P.; Mandal, A. K.; Catthoor, F.; Nag, M. Self-Aligned Amorphous Indium-Tin-Zinc-Oxide Thin Film Transistors on Polyimide Foil. *ECS J. Solid State Sci. Technol.* **2018**, *7*, P185–P191.

(10) Kim, B. K.; On, N.; Choi, C. H.; Kim, M. J.; Kang, S.; Lim, J. H.; Jeong, J. K. Polycrystalline Indium Gallium Tin Oxide Thin-Film Transistors with High Mobility Exceeding 100 cm2/Vs. *IEEE Electron Device Lett.* **2021**, *42*, 347–350.

(11) Cho, S. H.; Ko, J. B.; Ryu, M. K.; Yang, J.-H.; Yeom, H.-I.; Lim, S. K.; Hwang, C.-S.; Park, S.-H. K. Highly Stable, High Mobility Al:SnZnInO Back-Channel Etch Thin-Film Transistor Fabricated Using PAN-Based Wet Etchant for Source and Drain Patterning. *IEEE Trans. Electron Devices* **2015**, *62*, 3653–3657.

(12) Moreira, M.; Carlos, E.; Dias, C.; Deuermeier, J.; Pereira, M.; Barquinha, P.; Branquinho, R.; Martins, R.; Fortunato, E. Tailoring IGZO Composition for Enhanced Fully Solution-Based Thin Film Transistors. *Nanomaterials* **2019**, *9* (9), 1273–1314.

(13) Sheng, J.; Hong, T.; Lee, H. M.; Kim, K.; Sasase, M.; Kim, J.; Hosono, H.; Park, J. S. Amorphous IGZO TFT with High Mobility of Similar to 70 cm<sup>2</sup>/(V s) via Vertical Dimension Control Using PEALD. ACS Appl. Mater. Interfaces **2019**, *11*, 40300–40309.

(14) Powell, M. J.; Glasse, C.; Green, P. W.; French, I. D.; Stemp, I. J. An Amorphous Silicon Thin-Film Transistor with Fully Self-Aligned Top Gate Structure. *IEEE Electron Device Lett.* **2000**, *21*, 104–106.

(15) Fan, C.-L.; Shang, M.-C.; Li, B.-J.; Lin, Y.-Z.; Wang, S.-J.; Lee, W.-D. A Self-Aligned a-IGZO Thin-Film Transistor Using a New Two-Photo-Mask Process with a Continuous Etching Scheme. *Materials* **2014**, *7*, 5761–5768.

(16) Park, J. C.; Lee, H.-N.; Im, S. Self-Aligned Top-Gate Amorphous Indium Zinc Oxide Thin-Film Transistors Exceeding Low-Temperature Poly-Si Transistor. *ACS Appl. Mater. Interfaces* **2013**, *5*, 6990–6995.

(17) Fan, C.-L.; Tseng, F.-P.; Tseng, C.-Y. Electrical Performance and Reliability Improvement of Amorphous-Indium-Gallium-Zinc-Oxide Thin-Film Transistors with HfO2 Gate Dielectrics by CF4 Plasma Treatment. *Materials* **2018**, *11*, 824–828.

(18) Cho, Y.-J.; Shin, J.-H.; Bobade, S. M.; Kim, Y.-B.; Choi, D.-K. Evaluation of Y2O3 gate insulators for a-IGZO thin film transistors. *Thin Solid Films* **2009**, *517*, 4115–4118.

(19) Nam, Y.; Kim, H.-O.; Cho, S. H.; Ko Park, S. H. Effect of hydrogen diffusion in an In-Ga-Zn-O thin film transistor with an aluminum oxide gate insulator on its electrical properties. *RSC Adv.* **2018**, *8*, 5622–5628.

(20) Kim, Y.-M.; Lee, G.-W. Effects of Al2O3 gate insulator on the instability of amorphous indium-gallium zinc oxide thin film transistors. *AIP Adv.* **2018**, *8* (8), 1–7.

(21) Carlos, E.; Branquinho, R.; Martins, R.; Fortunato, E. New Challenges of Printed High-K Oxide Dielectrics. *Solid-State Electron.* **2021**, *183*, 108044.

(22) Li, G.; Abliz, A.; Xu, L.; Andre, N.; Liu, X.; Zeng, Y.; Flandre, D.; Liao, L. Understanding hydrogen and nitrogen doping on active defects in amorphous In-Ga-Zn-O thin film transistors. *Appl. Phys. Lett.* **2018**, *112* (25), 1–5.

(23) Ahn, B. D.; Shin, H. S.; Kim, H. J.; Park, J.-S.; Jeong, J. K. Comparison of the effects of Ar and plasmas on the performance of homojunctioned amorphous indium gallium zinc oxide thin film transistors. *Appl. Phys. Lett.* **2008**, *93*, 203506.

(24) Wang, H.; He, J.; Xu, Y.; Andre, N.; Zeng, Y.; Flandre, D.; Liao, L.; Li, G. Impact of hydrogen dopant incorporation on InGaZnO, ZnO and In2O3 thin film transistors. *Phys. Chem. Chem. Phys.* **2020**, 22, 1591–1597.

(25) Nomura, K.; Kamiya, T.; Hosono, H. Effect of Diffusion of Hydrogen and Oxygen on Electrical Properties of Amorphous Oxide Semiconductor, In-Ga-Zn-O. *ECS J. Solid State Sci. Technol.* **2013**, *2*, P5–P8.

(26) Hanyu, Y.; Domen, K.; Nomura, K.; Hiramatsu, H.; Kumomi, H.; Hosono, H.; Kamiya, T. Hydrogen passivation of electron trap in amorphous In-Ga-Zn-O thin-film transistors. *Appl. Phys. Lett.* **2013**, *103*, 202114.

(27) Kamal, R.; Chandravanshi, P.; Choi, D.-K.; Bobade, S. M. The effect of annealing in forming gas on the a-IGZO thin film transistor performance and valence band cut-off of IGZO on SiNx. *Curr. Appl. Phys.* **2015**, *15*, 648–653.

(28) Abliz, A. Effects of hydrogen plasma treatment on the electrical performances and reliability of InGaZnO thin-film transistors. *J. Alloys Compd.* **2020**, *831*, 154694–154697.

(29) Kim, D. H.; Jeong, H. S.; Lee, D. H.; Bae, K. H.; Lee, S.; Kim, M. H.; Lim, J. H.; Kwon, H. I. Quantitative Analysis of Positive-Bias-Stress-Induced Electron Trapping in the Gate Insulator in the Self-Aligned Top Gate Coplanar Indium-Gallium-Zinc Oxide Thin-Film Transistors. *Coatings* **2021**, *11*, 1192.

(30) Ko, J. B.; Yeom, H. I.; Park, S. H. K. Plasma-Enhanced Atomic Layer Deposition Processed SiO2 Gate Insulating Layer for High Mobility Top-Gate Structured Oxide Thin-Film Transistors. *IEEE Electron Device Lett.* **2016**, *37*, 39–42.

(31) Baek, I. H.; Pyeon, J. J.; Han, S. H.; Lee, G. Y.; Choi, B. J.; Han, J. H.; Chung, T. M.; Hwang, C. S.; Kim, S. K. High-Performance Thin-Film Transistors of Quaternary Indium-Zinc-Tin Oxide Films Grown by Atomic Layer Deposition. *ACS Appl. Mater. Interfaces* **2019**, *11*, 14892–14901.

(32) Lee, S. S. An Empirical Modeling of Gate Voltage-Dependent Behaviors of Amorphous Oxide Semiconductor Thin-Film Transistors including Consideration of Contact Resistance and Disorder Effects at Room Temperature. *Membranes* **2021**, *11* (12), 954–958.

(33) Barquinha, P.; Pimentel, A.; Marques, A.; Pereira, L.; Martins, R.; Fortunato, E. Effect of UV and Visible Light Radiation on the Electrical Performances of Transparent TFTs Based on Amorphous Indium Zinc Oxide. *J. Non-Cryst. Solids* **2006**, *352*, 1756–1760.

(34) Niang, K. M.; Barquinha, P. M. C.; Martins, R. F. P.; Cobb, B.; Powell, M. J.; Flewitt, A. J. A Thermalization Energy Analysis of the Threshold Voltage Shift in Amorphous Indium Gallium Zinc Oxide Thin Film Transistors Under Positive Gate Bias Stress. *Appl. Phys. Lett.* **2016**, *108*, 093505.

(35) Kim, W. G.; Tak, Y. J.; Ahn, B. D.; Jung, T. S.; Chung, K. B.; Kim, H. J. High-pressure Gas Activation for Amorphous Indium-Gallium-Zinc-Oxide Thin-Film Transistors at 100 degrees C. *Sci. Rep.* **2016**, *6*, 23039.

(36) Liu, W.-S.; Hsu, C.-H.; Jiang, Y.; Lai, Y.-C.; Kuo, H.-C. Improving Device Characteristics of Dual-Gate IGZO Thin-Film Transistors with Ar-O2Mixed Plasma Treatment and Rapid Thermal Annealing. *Membranes* **2021**, *12*, 49.

(37) Jeon, J. K.; Um, J. G.; Lee, S.; Jang, J. Control of O-H bonds at a-IGZO/SiO2 interface by long time thermal annealing for highly stable oxide TFT. *AIP Adv.* **2017**, *7*, 125110.

(38) Nomura, K.; Kamiya, T.; Hosono, H. Effects of Diffusion of Hydrogen and Oxygen on Electrical Properties of Amorphous Oxide Semiconductor, In-Ga-Zn-O. *ECS J. Solid State Sci. Technol.* **2013**, *2*, P5–P8.

(39) Nam, Y.; Kim, H.-O.; Cho, S. H.; Hwang, C.-S.; Kim, T.; Jeon, S.; Ko Park, S. H. Beneficial effect of hydrogen in aluminum oxide deposited through the atomic layer deposition method on the electrical properties of an indium-gallium-zinc oxide thin-film transistor. *J. Infect. Dis.* **2016**, *17*, 65–71.

(40) Wook Lee, Y.; Kim, S.-J.; Lee, S.-Y.; Lee, W.-G.; Yoon, K.-S.; Park, J.-W.; Han, M.-K. An Investigation of the Different Charge Trapping Mechanisms for SiNx and SiO2 Gate Insulator in a-IGZO TFTs. *Electrochem. Solid-State Lett.* **2012**, *15*, H84–H87.

(41) Lan, X.; Ou, X.; Lei, Y.; Gong, C.; Yin, Q.; Xu, B.; Xia, Y.; Yin, J.; Liu, Z. The interface inter-diffusion induced enhancement of the charge-trapping capability in HfO2/Al2O3 multilayered memory devices. *Appl. Phys. Lett.* **2013**, *103*, 192905.

(42) Kim, H. J.; Tak, Y. J.; Park, S. P.; Na, J. W.; Kim, Y.-G.; Hong, S.; Kim, P. H.; Kim, G. T.; Kim, B. K.; Kim, H. J. The self-activated

radical doping effects on the catalyzed surface of amorphous metal oxide films. *Sci. Rep.* 2017, 7, 12469.

(43) Park, S.-H. K.; Ryu, M.-K.; Oh, H.; Hwang, C.-S.; Jeon, J.-H.; Yoon, S.-M. Double-layerd passivation film structure of  $Al_2O_3/SiNx$ for high mobility oxide thin film transistors. *J. Vac. Sci. Technol., B* **2013**, 31, 020601.

(44) Kang, Y.; Ahn, B. D.; Song, J. H.; Mo, Y. G.; Nahm, H. H.; Han, S.; Jeong, J. K. Hydrogen Bistability as the Origin of Photo-Bias-Thermal Instabilities in Amorphous Oxide Semiconductors. *Adv. Electron. Mater.* **2015**, *1* (7), 1400006–1400013.

(45) Gaspar, D.; Pereira, L.; Gehrke, K.; Galler, B.; Fortunato, E.; Martins, R. High Mobility Hydrogenated Zinc Oxide Thin Films. *Sol. Energy Mater. Sol. Cells* **2017**, *163*, 255–262.

(46) Toda, T.; Wang, D. P.; Jiang, J. X.; Hung, M. P.; Furuta, M. Quantitative Analysis of the Effect of Hydrogen Diffusion From Silicon Oxide Etch-Stopper Layer Into Amorphous In-Ga-Zn-O on Thin-Film Transistor. *IEEE Trans. Electron Devices* **2014**, *61*, 3762–3767.

(47) Jeong, S.; Lee, J. Y.; Lee, S. S.; Seo, Y. H.; Kim, S. Y.; Park, J. U.; Ryu, B. H.; Yang, W.; Moon, J.; Choi, Y. Metal Salt-Derived In-Ga-Zn-O Semiconductors Incorporating Formamide as a Novel Co-Solvent for Producing Solution-Processed, Electrohydrodynamic-Jet Printed, High Performance Oxide Transistors. *J. Mater. Chem. C* **2013**, *1*, 4236–4243.

(48) Lee, S.; Nathan, A.; Jeon, S.; Robertson, J. Oxygen Defect-Induced Metastability in Oxide Semiconductors Probed by Gate Pulse Spectroscopy. *Sci. Rep.* **2015**, *5* (1), 14902–14910.

(49) Jeong, J.; Lee, G. J.; Kim, J.; Kim, J.; Choi, B. Oxygen Dispersive Diffusion Induced Bias Stress Instability in Thin Active Layer Amorphous In-Ga-Zn-O Thin-Film Transistors. *Appl. Phys. Express* 2013, *6*, 031101.

(50) Chang, Y. G.; Moon, T. W.; Kim, D. H.; Lee, H. S.; Kim, J. H.; Park, K. S.; Kim, C. D.; Im, S. DC Versus Pulse-Type Negative Bias Stress Effects on the Instability of Amorphous InGaZnO Transistors Under Light Illumination. *IEEE Electron Device Lett.* **2011**, *32*, 1704– 1706.

(51) Raja, J.; Jang, K.; Balaji, N.; Qamar Hussain, S.; Velumani, S.; Chatterjee, S.; Kim, T.; Yi, J. Aging Effects on the Stability of Nitrogen-doped, and Un-doped InGaZnO Thin-Film Transistors. *Mater. Sci. Semicond.* **2015**, *37*, 129–134.

(52) Singh, S.; Mohapatra, Y. N. Bias stress effect in solutionprocessed organic thin-film transistors: Evidence of field-induced emission from interfacial ions. *Org. Electron.* **2017**, *51*, 128–136.

(53) Lee, W. H.; Lee, S. J.; Lim, J. A.; Cho, J. H. Printed In-Ga-Zn-O drop-based thin-film transistors sintered using intensely pulsed white light. *RCS Adv.* **2015**, *5*, 78655–78659.

(54) Zhang, X.-H.; Tiwari, S. P.; Kippelen, B. Pentacene organic field-effect transistors with polymeric dielectric interfaces: Performance and stability. *Org. Electron.* **2009**, *10*, 1133–1140.

(55) Bae, M.; Yun, D.; Kim, Y.; Kong, D.; Jeong, H. K.; Kim, W.; Kim, J.; Hur, I.; Kim, D. H.; Kim, D. M. Differential Ideality Factor Technique for Extraction of Subgap Density of States in Amorphous InGaZnO Thin-Film Transistors. *IEEE Electron Device Lett.* **2012**, *33*, 399–401.

(56) Ide, K.; Nomura, K.; Hosono, H.; Kamiya, T. Electronic Defects in Amorphous Oxide Semiconductors: A Review. *Phys. Status Solidi A* **2019**, *216*, 1800372.

(57) Kim, H. W.; Kim, E. S.; Park, J. S.; Lim, J. H.; Kim, B. S. Influence of Effective Channel Length in Self-Aligned Coplanar Amorphous-Indium-Gallium-Zinc-Oxide Thin-Film Transistors with Different Annealing Temperatures. *Appl. Phys. Lett.* **2018**, *113*, 022104.

(58) Cho, S.-I.; Ko, J. B.; Lee, S. H.; Kim, J.; Park, S. H. K. Remarkably stable high mobility self-aligned oxide TFT by investigating the effect of oxygen plasma time during PEALD of SiO2 gate insulator. *J. Alloys Compd.* **2022**, *893*, 162308–162309.

(59) Jeong, S.-G.; Jeong, H.-J.; Choi, W.-H.; Kim, K. R.; Park, J.-S. Hydrogen Impacts of PEALD InGaZnO TFTs Using SiOx Gate Insulators Deposited by PECVD and PEALD. *IEEE Trans. Electron Devices* **2020**, *67*, 4250–4255.

(60) Kim, M.-H.; Choi, S.-Y.; Jeon, S.-H.; Lim, J.-H.; Choi, D.-K. Stability Behavior of Self-Aligned Coplanar a-IGZO Thin Film Transistors Fabricated by Deep Ultraviolet Irradiation. *ECS J. Solid State Sci. Technol.* **2018**, *7*, Q60–Q65.

(61) Jeong, W.; Winkler, J.; Schmidt, H.; Lee, K.-H.; Park, S.-H. K. Suppressing channel-shortening effect of self-aligned coplanar Aldoped In-Sn-Zn-O TFTs using Mo-Al alloy source/drain electrode as Cu diffusion barrier. *J. Alloys Compd.* **2021**, *859*, 158227–158312.